й«ҳеҲҶиҫЁзҺҮзӣёз§»

й…ҚзҪ®еҗҺCRCжӘўжҹҘ

жҸҗдҫӣXAжұҪи»ҠзүҲжң¬

й »зҺҮеҗҲжҲҗ����пјҢд№ҳжі•пјҢйҷӨжі•

иұҗеҜҢ����пјҢйқҲжҙ»зҡ„йӮҸијҜиіҮжәҗ

е°Ҳз”Ё18дҪҚд№ҳ18дҪҚд№ҳжі•еҷЁ

йӣҶжҲҗзҡ�18дҪҚй җ(yГ№)еҠ жі•еҷ�

еҸҜйҒёзҡ„зҙҡиҒ�(liГЎn)д№ҳжі•жҲ–MAC

дҪҺеҠҹиҖ—йҒёй …еҸҜйҷҚдҪҺйқңж…Ӣ(tГ i)йӣ»жөҒ

е…«еҖӢж•ё(shГ№)еӯ—жҷӮйҗҳз®ЎзҗҶеҷЁ(DCM)

ж¶ҲйҷӨжҷӮйҗҳеҒҸж–ң(延йҒІйҺ–е®ҡз’�(huГЎn))

еҲҶеұӨSelectRAM?еӯҳе„ІеҷЁжһ¶ж§�(gГІu)

иҲҮиЎҢжҘ�(yГЁ)жЁ�(biДҒo)жә�(zhЗ”n)PROMзҡ„й…ҚзҪ®жҺҘеҸ�

250 MHz XtremeDSP DSP48Aзү�

еңЁFPGAжҺ§еҲ¶дёӢеҠ ијүеӨҡеҖӢжҜ”зү№жөҒ

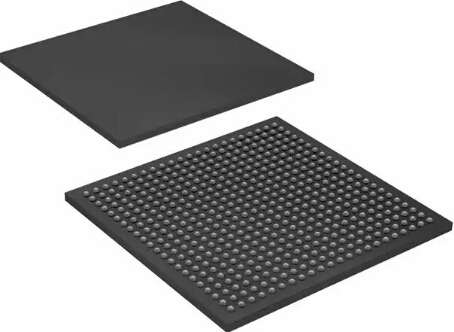

е…·жңүз„ЎйүӣйҒёй …зҡ„BGAе’ҢCSPе°ҒиЈқ

й«ҳйҒ”(dГЎ)373 Kbitзҡ„й«ҳж•ҲеҲҶеёғејҸRAM

жҺӣиө·пјҢдј‘зң жЁЎејҸжңғйҷҚдҪҺзі»зөұ(tЗ’ng)еҠҹиҖ�

йҖҡз”Ёе°ҒиЈқж”ҜжҢҒиј•жқҫйҖ�(jГ¬n)иЎҢеҜҶеәҰйҒ·з§�

е…·жңүJTAGзҡ„дҪҺжҲҗжң¬Xilinx?е№іиҮәй–ғеӯҳ

еҜ¬й »зҺҮиҢғең�(5 MHzиҮіи¶…йҒ�320 MHz)

еўһеј·(qiГЎng)зҡ„йӣҷеҖҚж•ё(shГ№)ж“�(jГ№)йҖҹзҺҮ(DDR)ж”ҜжҢҒ

еӨҡйӣ»еЈ����пјҢеӨҡжЁ�(biДҒo)жә�(zhЗ”n)SelectIO?жҺҘеҸЈеј•и…і

еӨҡйҒ”(dГЎ)519еҖӢI / Oеј•и…іжҲ�227еҖӢе·®еҲҶдҝЎиҷҹе°Қ

LVCMOS�����пјҢLVTTL�����пјҢHSTLе’ҢSSTLе–®з«ҜI / O

3.3V����пј�2.5Vпј�1.8V�пј�1.5Vе’�1.2VдҝЎд»Ө

еҸҜйҒёијёеҮәй©�(qЕ«)еӢ•еҷЁпјҢжҜҸеҖӢеј•и…іжңҖеӨ�24 mA

QUIETIOжЁ�(biДҒo)жә�(zhЗ”n)йҷҚдҪҺдәҶI / Oй–Ӣй—ң(guДҒn)еҷӘиҒІ

48дҪҚзҙҜеҠ еҷЁ�����пјҢз”ЁдәҺд№ҳжі•зҙҜеҠ�(MAC)ж“ҚдҪң

x8жҲ–x8 / x16 BPI并иЎҢNOR Flash PROM

IEEE 1149.1 / 1532 JTAGз·ЁзЁӢ/иӘ�(diГ o)и©Ұз«ҜеҸ�

дҪҺжҲҗжң������пјҢзҜҖ(jiГ©)зңҒз©әй–“зҡ„SPIдёІиЎҢй–ғеӯҳPROM

е”ҜдёҖзҡ„иЁӯ(shГЁ)еӮҷDNAжЁ�(biДҒo)иӯҳз¬Ұ�����пјҢз”ЁдәҺиЁӯ(shГЁ)иЁҲй©—иӯ�

DDR / DDR2 SDRAMж”ҜжҢҒжңҖй«�333 Mb / s

е®Ңе…Ёе…је®№32/64дҪ��пј�33/66 MHz PCIж”ҜжҢҒ

е®Ңе…Ё3.3VВұ10%зҡ„е…је®№жҖ§е’ҢзҶұжҸ’жӢ”е…је®№жҖ�

жҜҸеҖӢе·®еҲҶI / O 622+ Mb / sж•�(shГ№)ж“�(jГ№)еӮіијёйҖҹзҺҮ

й«ҳж•Ҳзҡ„еҜ¬еҫ�(fГ№)з”ЁеҷЁпјҢеҜ¬йӮҸијҜ���пјҢеҝ«йҖҹйҖ�(jГ¬n)дҪҚйӮҸиј�

йӣҷйҮҸзЁӢVCCAUXйӣ»жәҗз°ЎеҢ–дәҶеғ…3.3Vзҡ„иЁӯ(shГЁ)иЁ�

MicroBlaze?е’ҢPicoBlaze?еөҢе…ҘејҸиҷ•зҗҶеҷЁе…�(nГЁi)ж �

йӣҶжҲҗеҠ жі•еҷ������пјҢз”ЁдәҺеҫ©(fГ№)йӣңзҡ„д№ҳжі•жҲ–д№ҳжі•еҠ жі•йҒӢз®�

еҜҶеәҰй«ҳйҒ”(dГЎ)53712йӮҸијҜе–®е…ғ�пјҢеҢ…жӢ¬еҸҜйҒёзҡ„移дҪҚеҜ„еӯҳеҷ�

еҸҜз”Ёзҡ„з®Ўз·ҡзҙҡпјҢеңЁжЁ�(biДҒo)жә�(zhЗ”n)-4йҖҹеәҰзӯүзҙҡдёӢеҸҜеўһеј·(qiГЎng)иҮіе°‘250 MHzзҡ„жҖ§иғҪ

и¶…дҪҺжҲҗжң¬���пјҢй«ҳжҖ§иғҪDSPи§Јжұәж–№жЎҲпјҢйҒ©з”ЁдәҺеӨ§жү№йҮ���пјҢжіЁйҮҚжҲҗжң¬зҡ„жҮ�(yД«ng)з”�

еңЁBlock RAMдёҠжіЁеҶҠзҡ„ијёеҮә��пјҢеңЁжЁ�(biДҒo)жә�(zhЗ”n)-4йҖҹеәҰзӯүзҙҡдёӢиҮіе°‘д»Ҙ280 MHzйҒӢиЎҢ

й«ҳйҒ”(dГЎ)2268 Kbitзҡ„еҝ«йҖҹеЎҠRAM�пјҢе…·жңүеӯ—зҜҖ(jiГ©)еҜ«е…ҘеҠҹиғҪпјҢеҸҜз”ЁдәҺиҷ•зҗҶеҷЁжҮү(yД«ng)з”�

LVDS�����пјҢRSDS�����пјҢеҫ®еһӢLVDS��пјҢHSTL / SSTLе·®еҲҶI / O��пјҢеё¶жңүйӣҶжҲҗзҡ„е·®еҲҶзөӮз«Ҝйӣ»йҳ»

е…«еҖӢдҪҺеҒҸж–ңе…ЁеұҖжҷӮйҗҳз¶�(wЗҺng)зө�(luГІ)�пјҢжҜҸеҚҠеҖӢиЁӯ(shГЁ)еӮҷе…«еҖӢйЎҚеӨ–зҡ„жҷӮйҗҳ��пјҢд»ҘеҸҠиұҗеҜҢзҡ„дҪҺеҒҸж–ңи·Ҝз”�

жҷӮй–“пј�2023/8/4 17:10:49

жҷӮй–“пј�2023/8/4 17:10:49

й–ұи®Җпј�434

й–ұи®Җпј�434