гҖҖгҖҖDDR SDRAMиҲҮSDRAMзҡ„дёҚеҗҢдё»иҰҒй«”зҸ�(xiГ n)еңЁд»ҘдёӢе№ҫеҖ�(gГЁ)ж–№йқўпј�

гҖҖгҖҖ(1) еҲқе§ӢеҢ–гҖӮSDRAMеңЁй–Ӣ(kДҒi)е§ӢдҪҝз”ЁеүҚиҰҒйҖ�(jГ¬n)иЎҢеҲқе§ӢеҢ–��пјҢйҖҷй …(xiГ ng)е·ҘдҪңдё»иҰҒжҳҜе°Қ(duГ¬)жЁЎејҸеҜ„еӯҳеҷЁйҖ�(jГ¬n)иЎҢиЁӯ(shГЁ)зҪ���пјҢеҚіMRS��гҖӮDDR SDRAMиҲҮSDRAMдёҖжЁ���пјҢеңЁй–�(kДҒi)ж©�(jД«)жҷ�(shГӯ)д№ҹиҰҒйҖ�(jГ¬n)иЎҢMRS����пјҢдёҚйҒ�(guГІ)з”ұдәҺж“ҚдҪңеҠҹиғҪзҡ„еўһеӨҡпјҢDDR SDRAMеңЁMRSд№ӢеүҚйӮ„еўһеҠ дәҶдёҖеҖ�(gГЁ)ж“�(kuГІ)еұ•жЁЎејҸеҜ„еӯҳеҷЁиЁ�(shГЁ)зҪ�(EMRS)йҒ�(guГІ)зЁ���гҖӮйҖҷеҖ�(gГЁ)ж“�(kuГІ)еұ•жЁЎејҸеҜ„еӯҳеҷЁе°�(duГ¬)DLLзҡ„жңүж•ҲиҲҮзҰҒжӯў����гҖҒијёеҮәй©…(qЕ«)еӢ�(dГІng)еј�(qiГЎng)еәҰзӯүеҠҹиғҪеҜ�(shГӯ)ж–ҪжҺ§еҲ¶гҖ�

гҖҖгҖҖ(2) жҷ�(shГӯ)йҗ����гҖӮеүҚйқўд»Ӣзҙ№SDRAMжҷ�(shГӯ)已經(jД«ng)зңӢеҲ°����пјҢSDRAMзҡ„и®Җ/еҜ�(xiДӣ)йҮҮз”Ёе–®дёҖжҷ�(shГӯ)йҗҳгҖӮеңЁDDR SDRAMе·ҘдҪңдёӯиҰҒз”Ёе·®еҲҶжҷӮ(shГӯ)йҗ��пјҢд№ҹе°ұжҳҜе…©еҖ�(gГЁ)жҷ�(shГӯ)йҗҳпјҢдёҖеҖ�(gГЁ)жҳҜCLK���пјҢеҸҰдёҖеҖ�(gГЁ)жҳҜиҲҮд№ӢеҸҚзӣёзҡ„CK#гҖ�

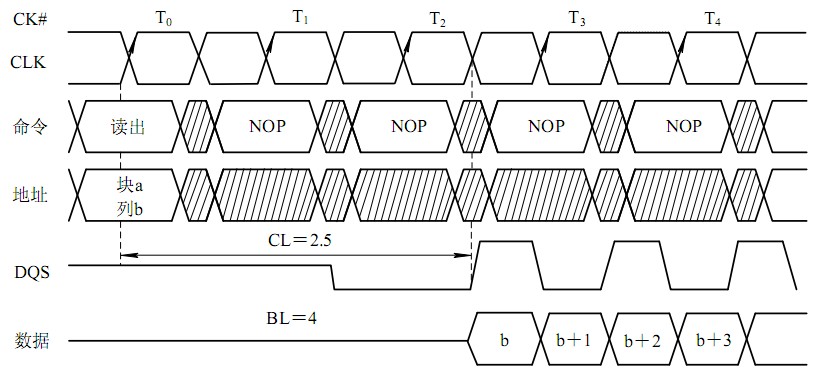

гҖҖгҖҖCK#并дёҚиғҪиў«зҗҶи§ЈзӮә第дәҢеҖ�(gГЁ)и§ёзҷј(fДҒ)жҷ�(shГӯ)йҗ�(еҸҜд»ҘеңЁи¬ӣиҝ°DDRеҺҹзҗҶжҷ�(shГӯ)з°�(jiЗҺn)е–®ең°йҖҷд№ҲжҜ”е–»)�����пјҢе®ғиғҪиө·еҲ°и§ёзҷ�(fДҒ)жҷ�(shГӯ)йҗҳж Ўжә�(zhЗ”n)зҡ„дҪңз”�����гҖӮз”ұдәҺж•ё(shГ№)ж“�(jГ№)жҳҜеңЁCLKзҡ„дёҠдёӢжІҝи§ёзҷј(fДҒ)зҡ„пјҢйҖ жҲҗеӮіијёе‘Ёжңҹзё®зҹӯдәҶдёҖеҚ�����пјҢеӣ жӯӨеҝ…й ҲиҰҒдҝқиӯүеӮіијёе‘Ёжңҹзҡ„з©©(wДӣn)е®ҡд»Ҙзўәдҝқж•�(shГ№)ж“�(jГ№)зҡ„жӯЈзўәеӮіијёпјҢйҖҷе°ұиҰҒжұӮе°�(duГ¬)CLKзҡ„дёҠдёӢжІҝй–“и·қиҰҒжңүзІҫзўәзҡ„жҺ§еҲ�����гҖӮдҪҶеӣ�?yГ n)й—Үеӣҹ?�гҖҒйӣ»йҳ»жҖ§иғҪзҡ„ж”№и®ҠзӯүеҺҹеӣ ���пјҢCLKдёҠдёӢжІҝй–“и·қеҸҜиғҪзҷј(fДҒ)з”ҹи®ҠеҢ–пјҢжӯӨжҷӮ(shГӯ)иҲҮе…¶еҸҚзӣёзҡ„CK#е°ұиө·еҲ°зіҫжӯЈзҡ„дҪңз”Ё(CLKдёҠеҚҮеҝ«дёӢйҷҚж…ў���пјҢCK#еүҮжҳҜдёҠеҚҮж…ўдёӢйҷҚеҝ«)�����гҖӮиҖҢз”ұдәҺдёҠдёӢжІҝи§ёзҷј(fДҒ)зҡ„еҺҹеӣ����пјҢд№ҹдҪҝCLпј�1.5жҲ�2.5жҲҗзӮәеҸҜиғҪпјҢ并容жҳ“еҜ�(shГӯ)зҸ�(xiГ n)�����гҖ�

гҖҖгҖҖ(3) ж•�(shГ№)ж“�(jГ№)йҒёеҸ–(DQS)и„ҲжІ–�����гҖӮDQSжҳҜDDR SDRAMдёӯзҡ„йҮҚиҰҒдҝЎиҷҹ(hГ o)��пјҢе…¶еҠҹиғҪдё»иҰҒз”ЁдҫҶ(lГЎi)еңЁдёҖеҖ�(gГЁ)жҷ�(shГӯ)йҗҳе‘Ёжңҹе…§(nГЁi)жә�(zhЗ”n)зўәең°еҚҖ(qЕ«)еҲҶеҮәжҜҸеҖ�(gГЁ)еӮіијёе‘ЁжңҹпјҢ并дҪҝж•ё(shГ№)ж“�(jГ№)еҫ—д»Ҙжә�(zhЗ”n)зўәжҺҘж”��гҖӮжҜҸдёҖеЎҠDDR SDRAMиҠҜзүҮйғҪжңүдёҖеҖ�(gГЁ)йӣҷеҗ‘зҡ„DQSдҝЎиҷҹ(hГ o)з·ҡгҖӮеңЁеҜ�(xiДӣ)е…ҘжҷӮ(shГӯ)�пјҢе®ғз”ЁдҫҶ(lГЎi)еӮійҖҒз”ұеҢ—ж©Ӣзҷ�(fДҒ)дҫ�(lГЎi)зҡ„DQSдҝЎиҷҹ(hГ o)пјӣеңЁи®ҖеҸ–жҷӮ(shГӯ)�пјҢеүҮз”ұиҠҜзүҮз”ҹжҲҗDQSеҗ‘еҢ—ж©Ӣзҷј(fДҒ)йҖ�?пјҹжўўе“үf(shuЕҚ)пјҢDQSе°ұжҳҜж•�(shГ№)ж“�(jГ№)зҡ„еҗҢжӯҘдҝЎиҷ�(hГ o)���гҖ�

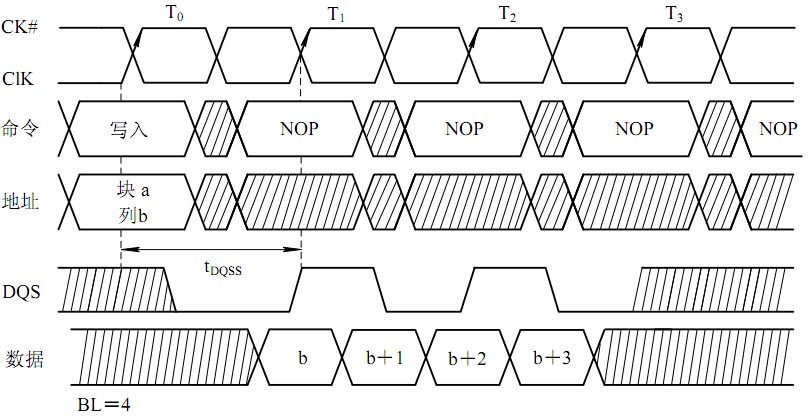

гҖҖгҖҖ(4) еҜ�(xiДӣ)е…Ҙ延жҷ�(shГӯ)�����гҖӮеңЁеҜ�(xiДӣ)е…ҘжҷӮ(shГӯ)пјҢиҲҮSDRAMзҡ�0延жҷӮ(shГӯ)дёҚдёҖжЁ������пјҢDDRSDRAMзҡ„еҜ«(xiДӣ)е…Ҙ延йҒІе·Із¶�(jД«ng)дёҚжҳҜ0дә��гҖӮеңЁзҷ�(fДҒ)еҮәеҜ«(xiДӣ)е…Ҙе‘Ҫд»ӨеҗҺпјҢDQSиҲҮеҜ«(xiДӣ)е…Ҙж•ё(shГ№)ж“�(jГ№)иҰҒзӯүдёҖж®өжҷӮ(shГӯ)й–“жүҚжң�(huГ¬)йҖҒйҒ”(dГЎ)�����гҖӮйҖҷеҖ�(gГЁ)е‘Ёжңҹиў«зЁұ(chД“ng)зӮәDQSзӣёе°Қ(duГ¬)дәҺеҜ«(xiДӣ)е…Ҙе‘Ҫд»Өзҡ„延йҒІжҷ�(shГӯ)й–“гҖ�

гҖҖгҖҖзӮәд»Җд№Ҳжңғ(huГ¬)жңүйҖҷжЁЈзҡ„延йҒІе‘ў��пјҹеҺҹеӣ д№ҹеңЁдәҺеҗҢжӯҘ�пјҢз•ўз«ҹеңЁдёҖеҖ�(gГЁ)жҷ�(shГӯ)йҗҳе‘Ёжңҹе…§(nГЁi)йҖ�(jГ¬n)иЎҢе…©ж¬ЎеӮійҖҒйңҖиҰҒеҫҲй«ҳзҡ„жҺ§еҲ¶зІҫеәҰпјҢе®ғеҝ…й ҲиҰҒзӯүжҺҘ收方еҒҡеҘҪе……еҲҶзҡ„жә�(zhЗ”n)еӮҷжүҚиЎ��гҖӮtDQSSжҳҜDDRе…�(nГЁi)еӯҳеҜ«(xiДӣ)е…Ҙж“ҚдҪңзҡ„дёҖеҖ�(gГЁ)йҮҚиҰҒеҸғж•ё(shГ№)пјҢеӨӘзҹӯзҡ„и©�(huГ )жҒҗжҖ•жҺҘ收жңүиӘ�����пјҢеӨӘй•�(zhЗҺng)еүҮжңғ(huГ¬)йҖ жҲҗзёҪз·ҡз©әй–‘гҖӮtDQSSжңҖзҹӯдёҚиғҪе°Ҹдә�0.75еҖ�(gГЁ)жҷ�(shГӯ)йҗҳе‘Ёжң����пјҢжңҖй•�(zhЗҺng)дёҚиғҪи¶…йҒҺ(guГІ)1.25еҖ�(gГЁ)жҷ�(shГӯ)йҗҳе‘Ёжң��гҖ�

гҖҖгҖҖ(5) зӘҒзҷј(fДҒ)й•�(zhЗҺng)еәҰиҲҮеҜ�(xiДӣ)е…ҘжҺ©зў�����гҖӮеңЁDDR SDRAMдёӯпјҢзӘҒзҷј(fДҒ)й•�(zhЗҺng)еәҰеҸӘжң�2����гҖ�4гҖ�8дёүзЁ®йҒёж“Ү���пјҢжІ’(mГ©i)жңүдәҶSDRAMзҡ„йҡЁж©�(jД«)еӯҳеҸ–зҡ„ж“ҚдҪ�(зӘҒзҷј(fДҒ)й•�(zhЗҺng)еәҰзӮә1)е’Ңе…Ёй �(yГЁ)ејҸзӘҒзҷ�(fДҒ)ж–№ејҸ��гҖӮеҗҢжҷ�(shГӯ)���пјҢзӘҒзҷ�(fДҒ)й•�(zhЗҺng)еәҰзҡ„е®ҡзҫ©д№ҹиҲҮSDRAMзҡ„дёҚдёҖжЁЈдәҶ���пјҢе®ғдёҚеҶҚжҢҮжүҖйҖЈзәҢ(xГ№)е°ӢеқҖзҡ„еӯҳе„�(chЗ”)е–®е…ғж•�(shГ№)йҮҸпјҢиҖҢжҳҜжҢҮйҖЈзәҢ(xГ№)зҡ„еӮіијёе‘Ёжңҹж•ё(shГ№)����гҖ�

гҖҖгҖҖе°�(duГ¬)дәҺзӘҒзҷ�(fДҒ)еҜ�(xiДӣ)е…ҘпјҢеҰӮжһңе…¶дёӯжңүдёҚжғіеӯҳе…Ҙзҡ„ж•�(shГ№)ж“�(jГ№)�пјҢд»ҚеҸҜд»ҘйҒ�(yГ№n)з”ЁDMдҝЎиҷҹ(hГ o)йҖ�(jГ¬n)иЎҢеұҸи”ҪгҖӮDMдҝЎиҷҹ(hГ o)е’Ңж•ё(shГ№)ж“�(jГ№)дҝЎиҷҹ(hГ o)еҗҢжҷӮ(shГӯ)зҷ�(fДҒ)еҮ����пјҢжҺҘ收方еңЁDQSзҡ„дёҠеҚҮжІҝиҲҮдёӢйҷҚжІҝдҫ�(lГЎi)еҲӨж–·DMзҡ„зӢҖж…�(tГ i)����пјҢеҰӮжһңDMзӮәй«ҳйӣ»е№і����пјҢйӮЈд№Ҳд№ӢеүҚеҫһDQSи„ҲжІ–дёӯйғЁйҒёеҸ–зҡ„ж•ё(shГ№)ж“�(jГ№)е°ұиў«еұҸи”Ҫдә���гҖ�

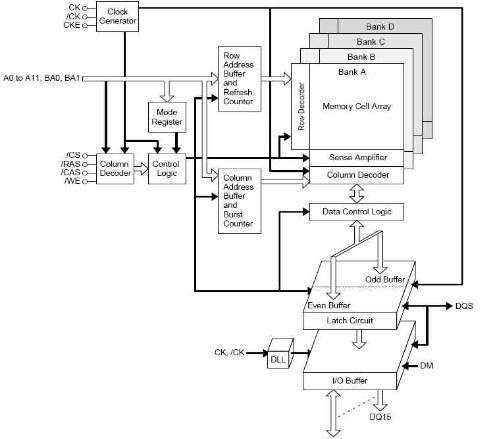

гҖҖ?���гҖ�?пјү延йҒІйҺ–е®ҡеӣһи·�(DLL)�гҖӮDDR SDRAMе°�(duГ¬)жҷ�(shГӯ)йҗҳзҡ„зІҫзўәжҖ§жңүи‘—еҫҲй«ҳзҡ„иҰҒжұӮ�пјҢиҖҢDDR SDRAMжңүе…©еҖ�(gГЁ)жҷ�(shГӯ)йҗҳпјҢдёҖеҖ�(gГЁ)жҳҜеӨ–йғЁзҡ„зёҪз·ҡжҷ�(shГӯ)йҗ��пјҢдёҖеҖ�(gГЁ)жҳҜе…§(nГЁi)йғЁзҡ„е·ҘдҪңжҷ�(shГӯ)йҗҳгҖӮеңЁзҗҶи«–дё������пјҢDDRSDRAMзҡ„йҖҷе…©еҖ�(gГЁ)жҷ�(shГӯ)йҗҳжҮү(yД«ng)и©ІжҳҜеҗҢжӯҘзҡ������пјҢдҪҶз”ұдәҺзЁ®зЁ®еҺҹеӣ �пјҢеҰӮжә«еәҰгҖҒйӣ»еЈ“жіўеӢ�(dГІng)иҖҢз”ў(chЗҺn)з”ҹ延йҒІдҪҝе…©иҖ…еҫҲйӣЈеҗҢжӯ�����пјҢжӣҙдҪ•жіҒжҷ�(shГӯ)йҗҳй »зҺҮжң¬иә«д№ҹжңүдёҚз©�(wДӣn)е®ҡзҡ„жғ…жіҒгҖӮйҖҷе°ұйңҖиҰҒж №ж“�(jГ№)еӨ–йғЁжҷ�(shГӯ)йҗҳеӢ•(dГІng)ж…�(tГ i)дҝ®жӯЈе…�(nГЁi)йғЁжҷӮ(shГӯ)йҗҳзҡ„延йҒІдҫ�(lГЎi)еҜ�(shГӯ)зҸ�(xiГ n)е…�(nГЁi)йғЁжҷӮ(shГӯ)йҗҳиҲҮеӨ–йғЁжҷ�(shГӯ)йҗҳзҡ„еҗҢжӯҘ���пјҢзӮәжӯӨе°Ҳ(zhuДҒn)й–Җ(mГ©n)иЁ�(shГЁ)зҪ®дәҶDLL�����гҖӮеҲ©з”ЁйҖҷзЁ®йӣ»и·Ҝ����пјҢеҸҜдҪҝе…§(nГЁi)йғЁжҷӮ(shГӯ)йҗҳиҲҮеӨ–йғЁжҷ�(shГӯ)йҗҳдҝқжҢҒеҗҢжӯҘгҖ�