ใใๅจๆฉ(jฤซ)ๆถๅๅ็ๆๅ�(wรน)ๅจไธญ็ๆ(yฤซng)็�

ใใ็ตๅคงๅคๆธ(shรน)็ๆๅ�(wรน)ๅจๅฏๅ็บๅ

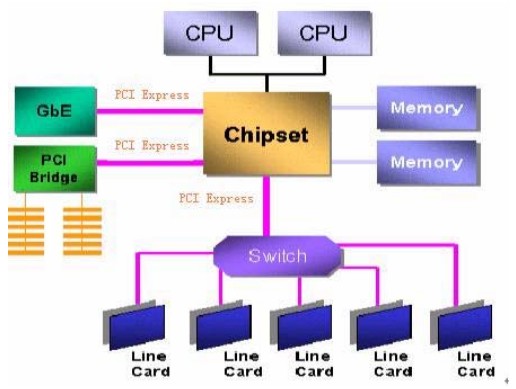

ฉ้กโI/Oๆๅ(wรน)ๅจๅ่จ�(jรฌ)็ฎๆๅ�(wรน)ๅ������ใไธ่ฌไพ่ช������๏ผI/Oๆๅ(wรน)ๅจๆๆ�1-2ๅ�(gรจ)CPUๅๅคๅ�(gรจ)I/Oๆๆงฝ��๏ผไปฅๅ้ฃๆฅๅฐI/O่ณๆบ็ๅ็จฎ่จญ(shรจ)ๅ����๏ผๅฆๅ

�(nรจi)ๅญ��ใ้ไฟก่จ�(shรจ)ๅ็ญ�����๏ผ่่จ(jรฌ)็ฎๆๅ�(wรน)ๅจๅๅ

ทๅๆดๅผท(qiรกng)็่จ(jรฌ)็ฎ่ฝๅ๏ผๅๅ�(gรจ)ๆๆดๅค็CPU๏ผๅ่ผๅฐ็I/O่ณๆบ�ใๅณ็ต�(tวng)็ๆฉ(jฤซ)ๆถๆๅ�(wรน)ๅจไธ่ฌ็บ19่ฑๅฏธๅฏ���๏ผ�1-4U้ซ��ใไฝๆฐ่็ๅ็ๆๅ�(wรน)ๅจๆญฃๆๅๅ

ถๆๆฌๅฐใๅ่ไฝ�����ใ้ซ็ฉๅฐๅ็ฎก็ๅฎนๆ็ญ็นๆง๏ผๅคง่ๆถๅ ๆฉ�(jฤซ)ๆถๆๅ�(wรน)ๅจ็ๅธๅ ด(chวng)ไปฝ้ก�ใ�

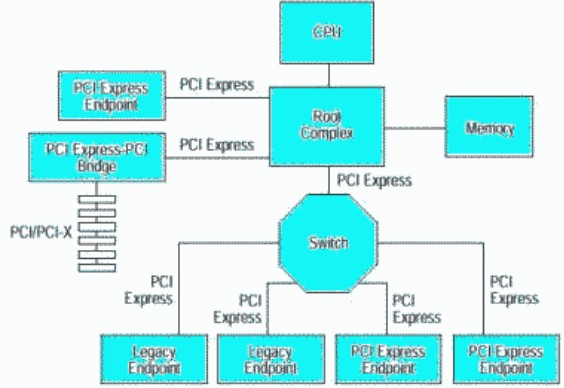

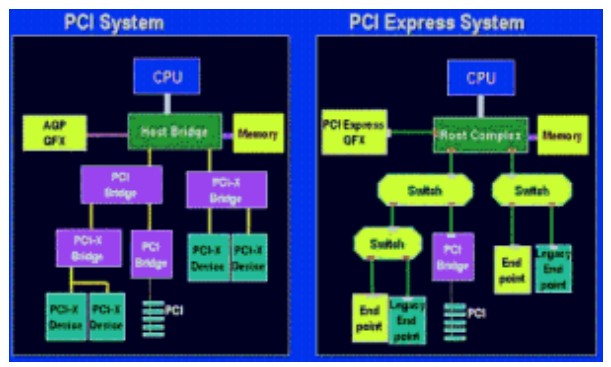

ใใๆๅ(wรน)ๅจไนๆไปฅ่ฝ(zhuวn)ๅPCIeๆ่ก�(shรน)๏ผๅฐฑๆฏ็บไบๅฉ็จPCIeๅจๅธถๅฏ������ใๅฏๆ�(kuรฒ)ๅฑๆ�����ใๅปฃๆณ็็ๆ

(tร i)ๅ็ญๆน้ข็ๅช(yลu)ๅ�(shรฌ)ใไปๅคฉๅธ้ขไธ็ๆๅ�(wรน)ๅจๅคง้ฝๆไพไธไบPCIeๆๆงฝ����๏ผ็ถ(dฤng)็ถๅคง้จๅ้ๆฏPCI-Xๆๆงฝ๏ผไฝๆๅ็ๅ����๏ผ้จ่่ฏ็็ตๅป ๅๅจ่ฏ็็ตไธ้ๆญฅๅๆถPCI-Xๆฅๅฃ�����๏ผPCIeๅไปฃPCI-Xๅทฒๆฏๆ�(shรญ)้ๅ้ก����ใ�

ใใๅผๅพไธๆ็ๆฏ๏ผๅฆไปๅธ้ขไธ็็ตๅคงๅคๆธ(shรน)่ฏ็็ต้ฝๆไพ3-4ๅ�(gรจ)ๆ�(shรน)็ฎๆ้็PCIe็ซฏๅฃ����๏ผไฝI(xiร n)/Oๅฏ้ๅๆ(yฤซng)็จ้กฏ็ถ้่ฆๆดๅค็PCIe็ซฏๅฃ����๏ผๅฆๅญๅฒ(chว)็ณป็ตฑ(tวng)����ใไบๆฏ๏ผๆไบๆๅ(wรน)ๅจๅป ๅๅฆPLXๅ

ฌๅธ�๏ผๅฐฑ้็ผ(fฤ)ไบๅธถๆๅคๅ�(gรจ)้้ๅ็ซฏๅฃ็PCIeไบคๆๅจ๏ผไปฅๅขๅ ๆๅ�(wรน)ๅจไธปๆฟไธ็PCIe็ซฏๅฃๆ�(shรน)���ใ�

ใใ้ๅธธ�๏ผๅ็ๆๅ�(wรน)ๅจๆไพSAS/SATA��ใๅ

็บ้้����ใๅๅ

ไปฅๅคช็ถฒ(wวng)็ญๅนพ็จฎๆฅๅ�����๏ผไปฅ้ฃๆฅ้ฃไบ็กๆณ่ขซๆๆๅ็ๆๅ

ฑไบซ็็ถฒ(wวng)็ต�(luรฒ)่จ�(shรจ)ๅๅๅญๅฒ(chว)่จ�(shรจ)ๅใไธๆๅทฒๆๅฐ๏ผๅ

จๆฐ็PCIeๅ�(xiรฉ)่ญฐๆฐๅขไบIOVๆ่ก�(shรน)���๏ผ้ๅฐๆธๅฐ้ฃๆฅๆ�(shรน)����๏ผๅฏฆ(shรญ)็�(xiร n)I/O่ณๆบ็ๅ

ฑไบซ๏ผๅพ่ๅฏไปฅๆฅตๅคงๅฐ้ไฝๆๅ(wรน)ๅจ็้่ณผ����ใ็ถญ่ญ�(hรน)ใๆฏๆๅ็ฎก็ๆๆฌ�ใ�

ใใๅจPCๅๅ่็ๆน้ข็ๆ(yฤซng)็�

ใใPCๅๅฝขๅกๆฏ้ฉ�(qลซ)ๅ�(dรฒng)PCIeๆ่ก�(shรน)็�(fฤ)ๅฑ็้�(guฤn)้ตๅ ็ด ใ�2006ๅน������๏ผ็ตๅคง้จๅ็้ซ็ซฏPCๆฉ�(jฤซ)้ฝๅ

ทๅไธๅ�(gรจ)x16 PCIeๆๆงฝ�๏ผไปฅๆฏๆ3Dใ้ซๅ่พจ็็ๅๅฝขๅๅๆๆ��ใ�

ใใPC่ฆ้ ปๆธธๆฒ็ถๅฆ้ซ้ๅ

ฌ่ทฏไธ็ๆฑฝ่ป���๏ผ็ผ(fฤ)ๅฑ้ๅบฆ้�?����๏ผ�?��๏ผ้กฏๅกๅป ๅไธๆท็ ๅถ้ซๅ่พจ็ๅๅ่็ๅ

ไปถ๏ผGPU๏ผ��๏ผไปฅๆ้ซ็กฌไปถๆง่ฝใๅฆไป���๏ผ้ซ็ซฏๅๅๆ่ก�(shรน)ๅจ็งๅญ�(xuรฉ)��ใๅจๆจไปฅๅๅทฅ็จ้ (lวng)ๅ็้่ฆๆงๅทฒๆฏ็กๅฏ้่ญ������ใGPUๅถ้ ๅไนๅธๆๆธธๆฒ็ผ(fฤ)็ๅๅ�?cรจ)่ถฆ่โ�(gรจ)x16 PCIeๆๆงฝไธๅฎ่ฃๅ

ฉๅ�(gรจ)GPU�๏ผไพๅฏ�(shรญ)็�(xiร n)ๆธธๆฒ้ซ้ฉ(yร n)ใ�

ใใๅจๅค้กฏ็คบๅจ่จ(jรฌ)็ฎไธญ็ๆ(yฤซng)็�

ใใๅค้กฏ็คบๅจ่จ�(jรฌ)็ฎๅๅๅถ้ฒ้ ญ่ง�����๏ผไปฅๅพๅค็จไบ้่ๅๅถๅ้ �(lวng)ๅ๏ผไฝ้จ่ๆๆฌ็้ไฝ��๏ผๆๆๆ็บไธ็จฎไธปๆต่ถจๅ�(shรฌ)���๏ผๅ

ถๆ�(yฤซng)็จ้ (lวng)ๅไธป่ฆๅ

ๆฌ๏ผ้ปๅญๆ�(shรน)ๆ�(jรน)่กจๅๆ็จๅบใๅบ็ๅฐๅ��ใCADใCAM���ใCAID�����ใๅทฅ็จ่ท่น����ใ็ถฒ(wวng)็ซ่จญ(shรจ)่จ�(jรฌ)��ใ็ถฒ(wวng)็ต�(luรฒ)ๆธธๆฒ���ใๆธธๆฒ้็�(fฤ)ใๆจกๅ่จญ(shรจ)่จ�(jรฌ)����ใๅๆฅ�(yรจ)ๆผ็คบใ้่ๅๆ��ใ่ก็ฅจไบคๆใ่ปไปถ้็�(fฤ)��ใๆจกๆฌไปฟ็�����ใ่ฆ้ ปๆ(huรฌ)่ญฐใๅ(dรฒng)็����ใ้ณ้ �/่ฆ้ ป็ทจ็ท็ญ็ญ����ใไฟ้�(jรฌn)้็จฎๆ�(yฤซng)็จๆจกๅผ็ผ(fฤ)ๅฑ็้�(guฤn)้ตๅ ็ด ๅจไบ๏ผPCIeๆ่ก�(shรน)ใๅ

จๆฐ็ๆไฝ็ณป็ตฑ(tวng)��ใๆดไฝ็ๅ

�(nรจi)ๅญๅน(jiร )ๆ ������ใLCDๆ่ก�(shรน)ๆน้�(jรฌn)�����ใ้กฏ็คบๅจๅ�(jiร )ๆ ผๅๆฐไธไปฃGPU่จ�(shรจ)ๅ�����ใ�

ใใๅจไธ่ฟฐ้ (lวng)ๅไธญ๏ผ็จๆถ็ๅทฅไฝ้่ฆๅๆ�(shรญ)ๅๅค็จฎๆ(yฤซng)็จ็จๅบๆไบค้����๏ผๅค้กฏ็คบๅจ่จ(jรฌ)็ฎๆญฃๅฅฝๅฏไปฅๅๆ�(shรญ)็่ฆฝๅ่็ๅคง้็ไฟกๆฏ่ณๆบใ้้ๅคๅ�(gรจ)้กฏ็คบๅ������๏ผ็จๆถๅฏไปฅๅจๅคๅ�(gรจ)้กฏ็คบๅฑไธ็งปๅ(dรฒng)ๅๆๅๅ็จฎไธๅ็ไฟกๆฏๅๅๅ����๏ผๅพ่ๆ้ซๅทฅไฝๆ็����ใ�

ใใๅจๅค้กฏ็คบๅจ่จ(jรฌ)็ฎ็้ณ้ ป/่ฆ้ ปๆ�(yฤซng)็จไธญ๏ผPCIeๆฅๅฃๆไพไบGPUๅ่็ๅจ๏ผ่ฏ็็ต๏ผ้็้ฃๆฅ��ใๅๆ�(shรญ)�๏ผไบคๆๅจๅฏไปฅ็จไพๆ�(kuรฒ)ๅฑไธป่็ๅจ๏ผๆ่

่ฏ็็ต๏ผไธ็PCIe็ซฏๅฃๆ�(shรน)๏ผ้�(jรฌn)่้ฃๆฅๅคๅ�(gรจ)GPU��ใ้ไฝฟๅพๆฟๅกๅถ้ ๅๅฏไปฅ่จ�(shรจ)่จ�(jรฌ)ๆดๅค็ๅๅฝข็ซฏๅฃ๏ผๆๆงฝ๏ผ������๏ผไปฅๆฏๆๅค้กฏ็คบๅจ็ณป็ตฑ(tวng)�ใ�

ใใๅจๅญๅ�(chว)็ณป็ตฑ(tวng)ๅ่ทฏ็ฑๅจไธญ็ๆ�(yฤซng)็�

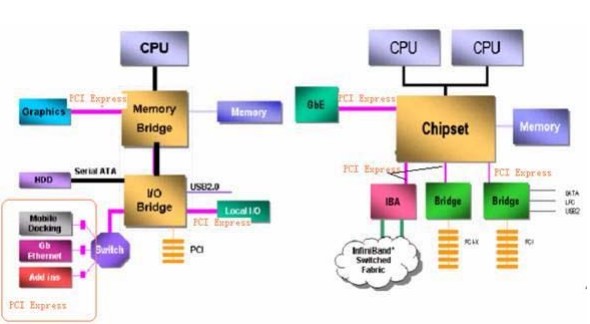

ใใไธๅ�(gรจ)ๅ

ธๅๅญๅฒ(chว)็ณป็ตฑ(tวng)ไพ้ CPUใๅ

ง(nรจi)ๅญ��ใI/O่ฏ็ใๆจกๅกๅๅญๅฒ(chว)่จ�(shรจ)ๅ้็้ซ้้ฃๆฅ�ใๅจๅฆไป็ๅพๅค็ณป็ต�(tวng)ไธญ๏ผPCIeๅฐฑๆไพไบFC�����ใSCSIใSATA็ญๅญๅ�(chว)ๆฅๅฃ่่็ๅจ้็้ฃๆฅ����๏ผๅพ่ๅฏฆ(shรญ)็�(xiร n)ๅฐ�(duรฌ)ๆดๅ�(gรจ)ๅญๅฒ(chว)็ณป็ตฑ(tวng)็ๆงๅถ็ฎก็ใ�

ใใๅ

็บ้้็ธฝ็ท้ฉ้

ๅจ๏ผHBA๏ผๅจไผๆฅญ(yรจ)็ด�(jรญ)ๅญๅฒ(chว)็ณป็ตฑ(tวng)ไธญๅ ๆ้่ฆๅฐไฝ�����ใ้ๅธธ๏ผHBA����ใFCใSCSI�ใSATAๅๅ

ถไปๆฅๅฃ้ฝ้็จๅณ็ตฑ(tวng)็PCI/PCI-X้ฃๆฅ็ธฝ็ท๏ผHBA้้่ฏ็็ต้ฃๆฅๅฐไธปๆฉ�(jฤซ)๏ผ้ฉ็จไบx86็ต�(jiรฉ)ๆง�(gรฒu)๏ผๆ่

็ดๆฅ้ฃๆฅไธปๆฉ(jฤซ)๏ผ้ฉ็จไบRISCๆถๆง(gรฒu)๏ผ��ใไฝ็บไบๆฏๆๆฅ็ๅข้ท็CPU้ๅบฆๅๅญๅ�(chว)ๆฅๅฃๆ�(shรน)ๆ�(jรน)็๏ผๅฉ็จPCI/PCI-X็ญๅณ็ต�(tวng)็ธฝ็ทไพ่จญ(shรจ)่จ�(jรฌ)็ณป็ตฑ(tวng)็ๆนๆณ้ๅงๅๅฐๅด(yรกn)้ๆๆ�(zhร n)��ใ่ไธ��๏ผ็บไบๅขๅ ๆๆงฝๆธ(shรน)้������๏ผ้้่ฆ้กๅค็PCI/PCI-Xๆฉๆฅๅจ๏ผๅพ่ๅธถไพไบ้กๅค็ๆๆ�����ใๅช้ณใๅพฉ(fรน)้ๆ��ใไธปๆฟ็ฉบ้ๅๅปถ้ฒ��ใๅณ็ต�(tวng)็ธฝ็ท็้ไบไธ่ถณๅปไฟ้�(jรฌn)ไบPCIe็ญไธฒ่กไบคๆๆ่ก�(shรน)็ๆฎๅ�����ใ�

ใใPCIeไบคๆๅจไธป่ฆ็จไบๆด(kuรฒ)ๅฑๅญๅ�(chว)็ณป็ตฑ(tวng)ไธปๆฟ็PCIe็ซฏๅฃๆ�(shรน)๏ผ็จไปฅ้ฃๆฅๆดๅค็ตไปถๆHBAไธ็ASIC����ใๅคๆ�(shรน)FC HBAๅป ๅ้ฝ่ฝ(zhuวn)ๅไบPCIeๆ่ก�(shรน)๏ผๅ ?yร n)ๆจ๎ๅณโ่๎ง่ชๆถ?๏ผๆๆๆด้ซ็ๅฏๆด(kuรฒ)ๅฑๅธถๅฏฌ๏ผๅฎๅ

จ็ฌฆๅFC็ท็๏ผ�1GB/s�����ใ�2GB/s�ใ�4GB/sๅ�8GB/s๏ผ็่ฆๆฑใ็พ(xiร n)ๅ��๏ผๅธๅ �(chวng)ไธ่จฑๅคๅป ๅ้ฝๆไพไบ็ธๆ�(yฤซng)็FC HBAๅSATAๅกใ�

ใใๅคงๅฎถ็ฅ้๏ผไบ่�(liรกn)็ถ�(wวng)้ฃๆฅไธป่ฆไพ้ ่ทฏ็ฑๅจ็ๆง่ฝ����๏ผ่ทฏ็ฑๅจๆงๅถ่ไฟกๆฏๆธ(shรน)ๆ�(jรน)๏ผๅ

๏ผๅจ็จๆถใ่จ(jรฌ)็ฎๆฉ(jฤซ)ๅ้ (yuวn)็จ็ณป็ต�(tวng)ไน้็ๅณ้������๏ผๅฆ็ถ�(wวng)ไธๆฒๆต���ใ้ตไป����ใftp็ญๆ(yฤซng)็������ใ้ซ็ซฏ่ทฏ็ฑๅจๆฏ็งๅฏไปฅ่็ๆ�(shรน)ไปฅ็พ่ฌ่จ(jรฌ)็ๆธ(shรน)ๆ�(jรน)ๅ�����๏ผๅพ่ๆปฟ่ถณ็พ(xiร n)ไปฃไฟกๆฏ็คพๆ�(huรฌ)ๅฐ�(duรฌ)่็้ๅบฆๅๅฏฆ(shรญ)ๆ�(shรญ)้ฟๆ(yฤซng)็่ๅป่ฆๆฑ�����ใ้ไบ่ทฏ็ฑๅจ็บ้ฉ�(yร n)่ญใๅฎๅ

�����ใๆๅ�(wรน)่ณ�(zhรฌ)้��ใ่ทฏ็ฑๅช(yลu)ๅไปฅๅ็ถฒ(wวng)็ต�(luรฒ)็ฎก็ๆไพ้�(yuวn)็จๅ

่็����ใไธไบๅฐ็จ่็ๅจๅๅฎๅถ็ASICไนๆ(huรฌ)ๅ่ๅ

ถไธญใ้ไบ่็ๅจๅASIC้่ฆ้้้ซ้ๆๆ็���ใ่ฏ็ๅฐ(duรฌ)่ฏ็ๆไธปๆฟๅฐ(duรฌ)ไธปๆฟ็ไบ่�(liรกn)ๆ่ก�(shรน)้�(jรฌn)่ก้ฃๆฅใ้ๅธธ���๏ผ่ทฏ็ฑๅจ็ฑ็ถฒ(wวng)ๅ����ใ่ทฏ็ฑๅจๆจกๅกๅๆงๅถๆจกๅก็ตๆใ�

ใใๅจๅทฅๆฅ�(yรจ)ๅตๅ

ฅๅผ็ณป็ต�(tวng)ไธญ็ๆ�(yฤซng)็�

ใใๅฆไป�����๏ผPCIeๅทฒ็ถ(jฤซng)่ขซ่จฑๅคๆจ(biฤo)ๆบ�(zhวn)็ต็น้็จ�����๏ผ็จไบๅทฅๆฅ�(yรจ)ๅตๅ

ฅๅผ้ (lวng)ๅ�����๏ผๅฆ้ซ็ซฏ้ปไฟก๏ผAdvanced Telecom๏ผ����ใๅพฎๅTCA็ณป็ตฑ(tวng)ๅAMC่ฆ�(guฤซ)ๆ ผใๅ

ถไธ��๏ผAMC้็จPCIe้ซ้ไธฒ่กๆฅๅฃ๏ผ็จไบๆฏๆๅพฎๅTCA็ณป็ตฑ(tวng)ไธญ็AMCๆจกๅกๅTCA็ณป็ตฑ(tวng)ไธญ็่ผๆณขๆจกๅก���ใAMCๆจกๅก่ขซ้ไฟก���ใ้ซ(yฤซ)็่จญ(shรจ)ๅใ่็ชฉๅบ็ซๅๆๅ็ณป็ตฑ(tวng)็ญ่จฑๅคๅตๅ

ฅๅผ็�(huรกn)ๅข้็������ใ�

ใใๅจๅบไบX86�ใMIPSใPowerPC็ญ่็ๅจ็็ณป็ต�(tวng)ไธ�����๏ผPCIeๆฅๅฃๆไพไบ่ฏ็็ตไธ็ไบ่ฏ(liรกn)ใPCIeไบคๆๅจๅ็จไบๆ�(kuรฒ)ๅฑ่ฏ็็ตๆ่็ๅจไธๆ้็็ซฏๅฃๆ�(shรน)�ใๆไบ็ณป็ต�(tวng)ๅฉ็จไบคๆๅจ็PTPๅ่ฝ้็ผ(fฤ)็ณป็ตฑ(tวng)่ๆฟๅไบคๆๆฉ(jฤซ)๏ผไปฅๆฏๆๆดๅค็I/O่จ�(shรจ)ๅ���ใ�

ใใ็บไบๆนไพฟ็ฎก็ๅๆงๅถ๏ผๅคงๅคๆ�(shรน)่ทฏ็ฑๅจๅป ๅ้็จๅณ็ต�(tวng)PCIไพ้ฃๆฅ่ทฏ็ฑๅจ็ๅญ็ณป็ต�(tวng)����ใ่ฟไพ๏ผ้จ่ๅฐ�(duรฌ)็ฎก็ๆจกๅกๅธถๅฏฌๅ่็่ฝๅ้ๆฑ็ๆฅ็ๅข้ท����๏ผ่ฟซไฝฟ่จญ(shรจ)่จ�(jรฌ)่

ๅฐๆฑๆฐ็ๆดๅฟซ้็ไบ่ฏ(liรกn)ๆ่ก�(shรน)ใ่PCIeๆ่ก�(shรน)็ฑไบๅฏไปฅๅPCIๅ

ผๅฎน��๏ผๆญฃๅฅฝๆไพไบ้ไธไพฟๅฉ���๏ผไธ็ก้ ๆดๆน็ถ�(wวng)็ต�(luรฒ)ๆไฝ็ณป็ตฑ(tวng)ใPCIeไบคๆๅจๅฏ็จไบ้ฃๆฅๅตๅ

ฅๅผ่็ๅจๅ็ถฒ(wวng)็ต�(luรฒ)่็ๅ��๏ผๅ ?yร n)ๆฆ่ ้�?shรน)่็ๅจ้ฝๆไพPCIeๆฅๅฃใ�

ใใๅฆไธๅ�(gรจ)ไพๅญๆ��๏ผๅณ็ต�(tวng)็ๅฎๅ

จ็ณป็ต�(tวng)ๅจๆงๅถ่ๅๅๅ่ฝไธ้ฝๆๅฑ้ๆง๏ผๆฏๅฆๅช่ฝ็ฐ�(jiวn)ๅฎๅฐๆชขๆธฌ(cรจ)้็ช้้�(guฤn)็ณป็ตฑ(tวng)�����ใไฝๆ่ฟๅนพๅน���๏ผ้ไบ็ณป็ตฑ(tวng)็ๅ่ฝๆไบ่ผๅคงๆนๅ������๏ผๅฆๅฏไปฅ้้ๆ็ทๆ็ก็ทๆๅๆฉ(jฤซ)๏ผๅฐ(duรฌ)ๅไฟ่ญ�(hรน)ๅ(qลซ)ๅไธญ็ๅคๅ�(gรจ)้ป�(diวn)้�(jรฌn)่ก่ฆ้ ป็ฃ(jiฤn)ๆงโโ็ฒๅ่ฆ้ ปๅ่ฑ������๏ผๅจๆฌๅฐๆฉ�(jฤซ)ไธ้�(jรฌn)่ก่็����๏ผ็ถๅๅณ้ๅฐไธปๆฉ(jฤซ)้�(jรฌn)่กๅๆ��ใ้กฏ็���๏ผ้ไนๅค้ซๅ่พจ็ๆๅๆฉ(jฤซ)ๅฐ�(duรฌ)็ณป็ตฑ(tวng)ๅธถๅฏฌๅๅๅ้ไนๆๅบไบๆด้ซ็่ฆๆฑ����๏ผ้่ฆๅคๅ�(gรจ)้ซ้็ซฏๅฃๅฐไฟกๆฏๅณ้็ตฆCPUๆไธปๆฉ�(jฤซ)�����ใPCIeไบคๆๅจๅ ?yร n)ๆฆญๆขข่ดๅณโๅๅฑc(diวn)ๅฐ�(duรฌ)้ป�(diวn)้ฃๆฅ����๏ผๆญฃๅฅฝๅฏไปฅๆผไบฎๅฐๆปฟ่ถณ้ไบ่ฆๆฑ��ใ�

ใใ็ถไธๆ่ฟ��๏ผPCI Express็ฑไบๆไพไบ้ซ้ๅธถๅฏ�����ใๅฏๆ�(kuรฒ)ๅฑ��ใๅปฃๆณ็็ๆ

(tร i)ๅใ่PCIๅ

ผๅฎน็ญ่ซธๅคๅช(yลu)ๅ�(shรฌ)�����๏ผๅ

ถๆ�(yฤซng)็จ่ๅๆญฃๅจๅพๅณ็ตฑ(tวng)็PCๅๅๅฝขๅทฅไฝ็ซ้ �(lวng)ๅๅๅคๆด(kuรฒ)ๅฑ��๏ผๅจๆๅ(wรน)ๅจใๅญๅ�(chว)�ใ่ทฏ็ฑใๅค้กฏ็คบๅจ่จ(jรฌ)็ฎไปฅๅๅทฅๆฅ�(yรจ)ๅตๅ

ฅๅผ็ณป็ต�(tวng)ไธญ้ฝๅพๅฐไบ้ๅธธๅปฃๆณ็ๆ�(yฤซng)็�����๏ผๅ

ถๅไปฃๅณ็ตฑ(tวng)็PCI/PCI-X็ธฝ็ทไนไธ้ๆฏๆ�(shรญ)้ๅ้กใ�